Pierwszy tranzystor był niewiele mniejszy od naszej dłoni. Po 70 latach od jego debiutu inżynierowie z IBM Research pokazali, że może mieć wielkość zaledwie 5 nm, czyli 0,000005 mm.

Krzemowy wafel z chipami wykonanymi w technologii 5 nm (zdjęcie: IBM Research)

Skala miniaturyzacji robi wrażenie, ale najbardziej istotny jest jej wymiar praktyczny. Mniejsze tranzystory oznaczają dłuży czas pracy na bateriach i większą wydajność smartfonów czy komputerów, bo są one podstawowym elementem, tworzącym mikroprocesory.

Replika pierwszego tranzystora

W 1965 roku Gordon Moore, będący jednym ze współtwórców firmy Intel, stwierdził, że liczba tranzystorów w procesorze – a co za tym idzie, jego moc obliczeniowa – będzie podwajać się co 18 miesięcy. Ta zależność, nazywana prawem Moore’a, wciąż jest aktualna, choć czas, w jakim następuje ten wykładniczy wzrost, został rozszerzony do dwóch lat.

Pierwszy historycznie mikroprocesor (Intel 4004), jaki trafił masowo na rynek w 1971 roku, mieścił w dość sporej obudowie 2300 tranzystorów i był wyprodukowany w procesie 10 μm. Oznacza to, że pojedynczy tranzystor miał ok. 10 000 nm czyli 0,01 mm szerokości. Teraz naukowcy z IBM Research przy współpracy z Samsungiem i firmą GlabalFoundries, produkującą chipy dla takich gigantów, jak AMD czu Qualcomm, stworzył pierwszy procesor wykonany w wymiarze technologicznym 5 nm. Pozwala to na umieszczenie na kawałku krzemowego wafla wielkości małego paznokcia 30… miliardów tranzystorów.

Tranzystory były płaskie, były przestrzenne…

Można powiedzieć, że do 2011 roku tranzystory polowe (FET), z jakich zbudowane były procesory, miały „płaską” poziomą konstrukcję. Taka budowa pozwoliła konstruktorom zminiaturyzować tranzystor do wielkości 32 nm. Na drodze do dalszej miniaturyzacji stanęły różnorakie zjawiska fizyczne, takie jak bariera potencjałów, prądy upływu (po przystępne napisane szczegóły odsyłam do ostatniego artykułu mojego kolegi, który o procesorach wiedział wszystko). Nie można już było dalej zmniejszać tranzystora, bo wiązałoby się to ze zredukowaniem wszystkich tworzących go komponentów. Najbardziej problematyczna była i jest tutaj szerokość kanału, od której zależy maksymalny prąd, jaki może przez niego popłynąć.

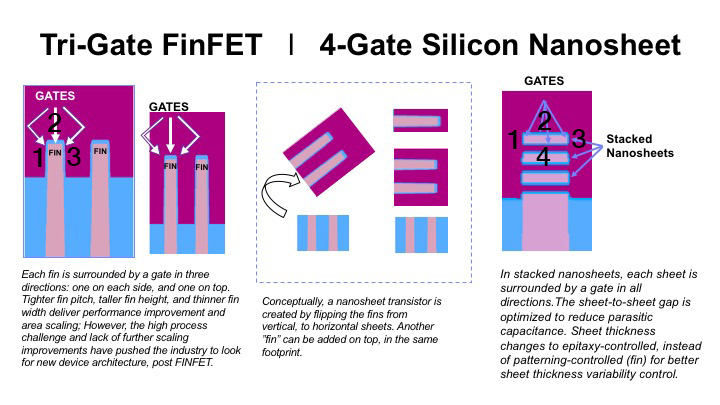

Dlatego, aby po raz kolejny zmniejszyć tranzystor należało go inaczej zbudować. Jako pierwszy zrobił to wtedy właśnie Intel i to co do tej pory płasko leżało na krzemowym waflu postawił pionowo. Tak narodził się FinFET, czyli tranzystor, którego kanał miał postać pionowego żebra lub żeber w celu zwiększenia jego wydajności (im większa powierzchnia kontaktu z bramką tym lepiej). Dobrze to widać na poniższym filmie:

Wertykalizacja pozwoliła wtedy zmniejszyć wymiar technologiczny do 22 nm, by przez kolejne lata dojść do wymiaru 10 nm, w jakim robione będą seryjnie procesory do smartfonów przez Samsunga. IBM poszedł dalej i pokazał, że jest w stanie wyprodukować nawet 7 nm tranzystor wykorzystując w tym celu do stworzenia krzemowych chipów technologię fotolitografii EUV (ekstremalny ultrafiolet, o czym jeszcze za chwilę). Niemniej FinFET tym samym zbliżył się do swojego kresu. Potrzeba było czegoś nowego.

… teraz będą otoczone.

IBM wpadł na pomysł, by ponownie uczynić tranzystor płaskim. Pionowe żebra od pewnego momentu już nie mogą być ani węższe, ani wyższe, bo mogłyby się przechylić, jak trawa i się zetknąć. Dlatego pionowe kanały ponownie zotały ułożone horyzontalnie i otoczony bramką. by zapewnić im maksymalną wydajność. Tak powstał GAAFET czyli Gate All Around FET.

Tak zbudowano tranzystor GAAFAT (zdjęcie: IBM Research)

Procesory wyprodukowane w technologii 5 nm, w stosunku do dostępnej na rynku technologii 10 nm, według IBM zapewniają 40-procentowy wzrost wydajności lub 75-procentową oszczędność energii przy zoptymalizowaniu wydajności.

Nie byłoby to jednak możliwe bez wykorzystania procesu litografii EUV. Wcześniej stosowana fotolitografia impresyjna, która do tworzenia krzemowego wafla wykorzystywała laser pracujący ze światłem o długości fali 193 nm. EUV pracuje z światłem o długości 13,5 nm! I już wiadomo, że dzięki użyciu tej techniki tworzenia procesorów powinno się udać zejść do wymiaru 3 nm. Problem tylko w tym, że naświetlarka EUV waży ok. 180 ton i do swojej pracy potrzebuje zasilania o mocy 1 MW, litografia immersyjna zaś „tylko” 165 kW.

Z jednej strony EUV upraszcza proces tworzenia krzemowego wafla, bo w przeciwieństwie do starszej technologii, całą strukturę może stworzyć, jak przypadku IBM-a, za jednym naświetleniem. Z drugiej strony cały proces jest zdecydowanie bardziej kosztowny.

Przygotowywanie testowych wafli (zdjęcie: IBM Research)

Na chwilę obecną nie wiadomo co nas czeka po premierze procesora z 3 nm tranzystorem. Jak na razie, na drugą połowę roku, Intel zapowiedział sprzedaż 18-rdzeniowego procesora, który będzie produkowany w technologii 14 nm. Oznacza to, że giganci mają jeszcze kilka nanometrów przed sobą. Jednak eksperci są zgodni, że ograniczenia wynikające z praw fizyki mniej więcej w 2021 roku doprowadzą do kresu wymiar pojedynczego tranzystora. Nie znaczy to jednak, że przestanie działać prawo Moore’a – przecież chipy można układać jeden na drugim…

Musisz być zalogowany, aby dodać komentarz.